|

指令集的发展史 而说到指令集的发展,就不得提到目前主流处理器所采用的X86架构。所谓X86架构的处理器就是采用了Intel X86指令集的处理器,X86指令集是Intel公司为其第一块16位处理器i8086所专门开发的。而IBM在1981年所推出的第一台PC机上所使用的处理器i8088(i8086的简化版)也是使用的X86指令集,但是为了增加计算机的浮点运算能力,增加了X87数学协助处理器和加入了X87指令集,于是就将采用了X86指令集和X87指令集的处理器统称为X86架构的处理器。

第一块支持X86指令集的Intel i8086处理器 到目前为止,Intel公司所生产的大部分处理器都是属于X86架构的处理器,包括像i80386、i80486和Pentium系列处理器等等。而Intel公司以外,AMD和Cyrix等厂商也在生产集成了X86指令集的处理器产品,而这些处理器都能够与支持Intel处理器的软件和硬件相兼容,所以也就形成了今天庞大的X86架构的处理器阵容。 然而随着处理器技术的发展,虽然处理器的主频和制造工艺都有一定的进步,但是处理器的性能确不能非常明显的提高,其中一个非常重要的原因就是受到了X86所采用的SISC指令集的限制。这一点Intel方面也非常清楚。而目前IA-32(Intel Architechure-32 英特尔32位体系架构)的X86系列处理器存在着一系列的问题,使得Intel方面已经打算放弃X86指令体系处理器的发型,而将重点放在下一代的IA-64体系处理器和EPIC(Explicitly Parallel Instruction Computing)显性并行指令方面。

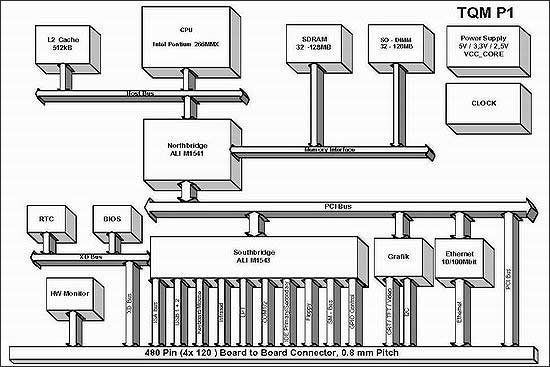

X86架构处理器示意图 首先,我们要知道,提高处理器每个时钟频率的指令执行数来提高处理器的性能,而这也是Intel开发新指令集的主要目的,这样一来,处理器可以让指令更容易解码,并且更容易进行并行处理,这样就可以不受指令集的限制来开发新型的处理器。而X86指令集的劣势就在于它的限制过多。 第一、由于X86指令集是属于CISC类型的指令集,其每条指令的长度是不固定的,而且有几种不同的格式,这样一来,就造成了X86处理器的解码工作非常复杂。而为了提高处理器的工作频率,就不得不延长处理器中的流水线,而过长的流水线在分支如果出现预测出错的情况,又会带来CPU工作停滞时间较长的弊端。 第二、X86指令采用了可访问内存地址的方法,这样的方法容易造成处理器与内存之间的不平衡工作,从而降低处理器的工作效率。而先进的RISC处理器则是使用Load/Store的存储模式,其中只有Load和Store指令才能从内存中读取数据到寄存器,所有其他指令只对寄存器中的操作数进行计算。 第三、X86构架处理器中的FPU(Floating Point Unit)浮点运算单元的运算能力较差,可以说现今市面上所有类型处理器中最慢的,其主要原因就是X86指令集中所使用的一个操作数堆栈。如果在运算过程中,没有足够的寄存器进行计算,系统就不得不使用堆栈来存放数据,这样一来会浪费大量的时间来处理FXCH指令,就是将正确的数据放到堆栈的顶部。 第四、X86指令对于各种扩展部件的限制也是十分不利的。首先,X86架构的处理器对于4GB的内存容量上限制,虽然现在目前主流的个人电脑的内存大小为512MB和1GB,但是相信随着操作系统和应用软件的不断提升,会快将会突破4GB的内存容量。另外,由于为了提高X86架构的处理器的性能,而出现像寄存器重命名、缓冲器巨大、乱序执行、分支预测、X86指令转化等等现象,都使得处理器的核心面积变得越来越大,这也限制了处理器工作频率的进一步提升,此外,处理器所集成的这些庞大数目的晶体管都只是为了解决X86指令的问题,所以继续采用X86架构必将会影响到处理器的发展。 而反观IA-64体系,由于采用了RISC指令集,可由一个指令、两个输入寄存器和一个输出寄存器组成,指令只对寄存器进行操作。并且具有多个不同的流水线或执行单元,能够并行执行许多指令。在对指令的处理速度上要明显优于CISC类型的IA-32体系。 而Intel的Merced(也就是现在Itanium安腾)处理器就是一块采用IA-64体系的64位处理器。它拥有64位寻址能力和64位位宽的寄存器,所以称之为64位处理器。由于具有64位寻址能力,Merced能够使用1百万TB(1TB=1024GB)的地址空间,足以运算企业级的数据任务,64位宽的寄存器可以使Merced 达到非常高的精度和运算速度。它所采用的EPIC指令可以使得处理器进行并行处理,在相同的时钟周期内,采用并行处理的指令执行数是普通CISC指令集的两倍。此外,Merced可进行并行分支预测。在目前的普通的处理器中,分支预测的正确率可以达到90%~95%,虽然正确率已经相当高了,但如果预测出错时,处理器就不得不清洗整条流水线,从而降低处理器的运算效率。10%的预测出错率会让处理器损失近30%的性能,而且如果流水线越长的情况下,性能损失就越严重。而Merced的所采用的预测机制,可以使分支都能进行并行执行,而且所花的招待时间与执行单个分支的时间是相同的。其次,处理器不会再冒预测出错的风险。由于处理器不再进行跳跃执行,它不会把程序代码分成一个一个的小块。而是将稍前和稍后的程序代码进行打包,然后一起将它们发布,加强了并行工作量。这些可以使采用EPIC指令的处理器避免普通处理器所出现的分支预测40%的出错情况,从而使处理器的性能提高10%~15%,特别是在整数代码部分。

Intel的Merced处理器 (责任编辑:admin) |